# A Comparative Study of Total Harmonic Distortion betweenTwo Topologies 27- and 31 Multi Level Inverter

Muna Hassan Husien muna.20enp54@student.uomosul.edu.iq Mohammed Ali AL-rawi mauom@uomosul.edu.iq

Electrical Engineering Department, Collage of Engineering, University of Mosul, Mosul, Iraq

Received: 2022-8-3 Received in revised form: 2022-9-1 Accepted: 2022-10-26

## ABSTRACT

In recent times, Multilevel inverters are considered an essential component of power electronics with widespread use in a wide range of high-voltage and high-power industrial and commercial applications. The use of multi-level inverters, also known as MLIs, has been preferred over conventional inverters due to the characteristics that these MLIs possess. These characteristics include low harmonic distortion caused by satisfacory performance of MLIs. This paper is concerned with analyzing harmonics to gain a deeper understanding of the performance of cascaded H-Bridge multilevel inverters (CHB-MLI). The model was constructed by using MATLAB/SIMULINK. A comparison was made between an asymmetrical cascaded 27 and 31-level multi-level inverter (MLI) by using the Phase disposition sinusoidal Pulse Width Modulation (PD-SPWM)and Phase Opposition Disposition sinusoidal Pulse Width Modulation (PD-SPWM)and Phase Opposition Disposition sinusoidal Pulse Width Modulation (PD-SPWM) techniques. According to the outcomes of the simulations, 31 levels are better than 27 where Total Harmonic Distortion (THD) in 31 levels is lower than 27 levels. The best result obtained during this study is 31 levels that use (PD-SPWM) technology, where the percentage of total harmonic distortion is small compared to the results and equal to 3.63%.

## Keywords:

Multilevel inverter, phase disposition sinusoidal Pulse Width Modulation (PD-SPWM), Total Harmonic Distortion, Phase Opposition Disposition sinusoidal Pulse Width Modulation (POD-SPWM) Asymmetrical multi-level inverter (AML).

This is an open access article under the CC BY 4.0 license (<u>http://creativecommons.org/licenses/by/4.0/</u>). https://rengj.mosuljournals.com

## 1. INTRODUCTION

Multi-level inverters have a greater number of benefits when compared to conventional two-level inverters [1,2], multilevel inverters have gained popularity in high power, and medium voltage applications because they may be used without a transformer and with less noise and harmonic distortion.

The primary benefits of multilevel inverters (MLIs) include lower total harmonic distortion (THD) in output voltage because of the many levels of the waveform, lower switching frequency which results in lower switching losses, the use of switches with lower voltage ratings to achieve higher output voltage. In addition, DV/DT stress is being little, which leads to a reduction in electromagnetic coupling [3,5].

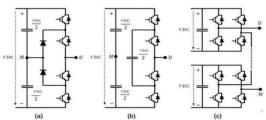

Increasing the number of levels results in the formation of a very fine ladder state wave that is closer to the intended sine wave, and as a result, the total harmonic distortion (THD) reduces [4]. . multi-level inverters are divided into three types: 1) diode clamped 2) flying capacitors, 3) cascade H -bridge [6,7]. It has been determined that the H-Bridge cascade inverter is the most suitable option for both the grid and photovoltaic systems (CHB-MLI) [5]. The H-shaped cascading multilevel inverter is created with fewer components and is designed to bridge quickly when compared to other multi-level inverters. Figure 1 illustrates types of MLI. Figure 1(a) shows a three-level diode clamped, and Figure 1 (b) shows a three-level flying capacitor.

Fig.1 One leg of multi-level inverter topology

Figure(1,c), shows the structure Cascaded H-bridge inverter in which each cell is separated from the others and feeds these separated cells from several different DC sources[9].

In addition, each cell generates three different voltage levels (VDC, 0,-VDC) .In comparison to other kinds of inverters, the Cascaded Bridge multi-level inverter is distinguished by its high level of dependability as well as its user-friendly control [10]. Cascaded H-bridge MLI includes two types: symmetric and asymmetric. If voltage sources are equal, the CHB is symmetrical MLI. And the level of the output voltage can be determined in this case by applying the following equation:

## m = 2n+1

#### where n: denotes the total number of H-bridges

m: indicates the total number of levels.

If dc-sources are different, the CHB is asymmetrical. The major advantage of the asymmetric CHB topology is that it can considerably increase the number of output voltage levels by using few dc voltage sources and IGBTs or MOSFETs.While symmetric Cascaded MLI, the voltage is the same in every cell and the voltage increases by increasing the number of cells. In this paper, a basic 27 and 31 single-phase asymmetric multilevel inverters are discussed.

Table (1) shows the comparison between three types of MLI topologies [19].

| S<br>·<br>N | Characteristic<br>s         | Cascade<br>d H-<br>Bridge | Bridge<br>Diode<br>Clamped | Flying<br>Capacitor |

|-------------|-----------------------------|---------------------------|----------------------------|---------------------|

| 1           | Main<br>switching<br>device | 2(m-1)                    | 2(m-1)                     | 2(m-1)              |

| 2           | Main<br>Diodes              | 2(m-1)                    | 2(m-1)                     | 2(m-1)              |

| 3           | Clamping<br>Diodes          | 0                         | (m-1)(m-<br>2)             | 0                   |

| 4           | DC bus                      | (m-1)/2                   | ( <b>m-1</b> )             | ( <b>m-1</b> )      |

Table 1: comparison of topologies

|   | •.          |          |          |                           |

|---|-------------|----------|----------|---------------------------|

|   | capacitor   |          |          |                           |

| 5 | Balancing   | 0        | 0        | ( <b>m-1</b> )( <b>m-</b> |

|   | Capacitor   |          |          | 2)/2                      |

| 6 | Redundan    | Redundan | Not      | Redundant                 |

|   | су          | t        | Redundan |                           |

|   | -5          |          | t        |                           |

| 7 | DC Bus      | Separate | DC Bus   | DC Bus                    |

|   | Sharing     | DC       | Sharing  | Sharing                   |

| 8 | Structure   | Modular  | Not      | Not                       |

|   |             |          | Modular  | Modular                   |

| 9 | Flexibility | Flexible | Not      | Not                       |

|   |             |          | Flexible | Flexible                  |

#### **Modulation Technique**

Multi-Carrier modulation PWM includes two methods that are commonly used and can be categorized as:

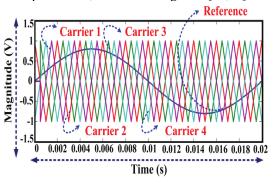

### 1. Phase shift multicarrier Modulations

In this technique, multi-carrier waves and one sine wave will be needed [12]. In general, for a multi-level inverter with n level, the number of triangular waves is required (n-1), Where n represents the number of cells in each phase. All triangular carriers in the Phase shift have the same frequency and peak-to-peak amplitude but they show phase shift, as shown in figure 2 [16,13].

Fig. 2 PhaseShift –PWM

#### 2. Level –shifted Multicarrier Modulation

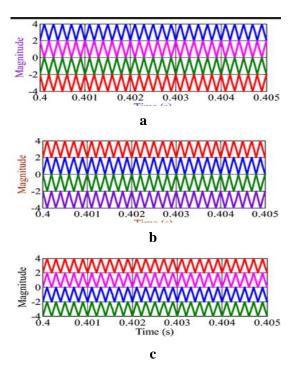

An m-level CHB inverter employing a level-shifted multi-carrier modulation technique, similar to phase-shifted modulation, requires (m - 1) triangular carriers with the same frequency and amplitude but doesn't have a phase shift. This type is divided into three techniques:

•Alternative Phase Opposite DispositionModulation: Through a (figure 3.a), we notice that in this type, each triangular wave is the opposite of the next wave [17,18].

• Phase Opposition Disposition: In this type of level shift technique, the lower waves are opposite to the upper waves, that is, the waves above zero are in the same phase, and the lower waves that are below zero are in the same phase as shown in (figure 3.b)

• Phase disposition: in this technique, all carriers are in phase [18], demonstrated in (figure 3.c)

Figure3. LS-PWM carrier arrangements: a) PD, b) POD, c) APOD

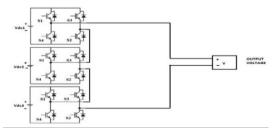

#### MULTILEVEL INVERTER TOPOLOGIES 1.Basic twenty seven Cascaded H-bridge asymtric Multilevel inverter

The basic configuration of a 27-level Cascaded H-bridge Multi-Level Inverter is illustrated in figure(4). The proposed DC-AC cascaded H-bridge multilevel inverter's topology. where The inverter uses three H bridges with three unequal DC sources, and the values of sources the following are in ratios:1VDC:3VDC:9VDC. This structure can only produce twenty-seven levels with a range from+13 to -13 including zero voltage, Table.2 illustrates switching cases in the 27-levels to create different voltages between +13 and -13.

Fig 4. 27 level Cascaded H-Bridge Multilevel inverter

|              | Switches in Cascaded H-Bridge 27 level MLI |    |            |        |        |        |        |        |        |             |             |             |

|--------------|--------------------------------------------|----|------------|--------|--------|--------|--------|--------|--------|-------------|-------------|-------------|

| Vo           | S<br>1                                     | S2 | <b>S</b> 3 | S<br>4 | S<br>5 | S<br>6 | S<br>7 | S<br>8 | S<br>9 | S<br>1<br>0 | S<br>1<br>1 | S<br>1<br>2 |

| +13<br>V     | 1                                          | 1  | 0          | 0      | 1      | 1      | 0      | 0      | 1      | 1           | 0           | 0           |

| +12<br>V     | 1                                          | 0  | 1          | 0      | 1      | 1      | 0      | 0      | 1      | 1           | 0           | 0           |

| +11<br>V     | 0                                          | 0  | 1          | 1      | 1      | 1      | 0      | 0      | 1      | 1           | 0           | 0           |

| +10<br>V     | 1                                          | 1  | 0          | 0      | 1      | 0      | 1      | 0      | 1      | 1           | 0           | 0           |

| +9<br>V      | 1                                          | 0  | 1          | 0      | 1      | 0      | 1      | 0      | 1      | 1           | 0           | 0           |

| +8<br>V      | 0                                          | 0  | 1          | 1      | 1      | 0      | 1      | 0      | 1      | 1           | 0           | 0           |

| +7<br>V      | 0                                          | 0  | 1          | 1      | 0      | 0      | 1      | 1      | 1      | 1           | 0           | 0           |

| +6<br>V      | 1                                          | 0  | 1          | 0      | 0      | 0      | 1      | 1      | 1      | 1           | 0           | 0           |

| +5<br>V      | 0                                          | 0  | 1          | 1      | 0      | 0      | 1      | 1      | 1      | 1           | 0           | 0           |

| +4<br>V      | 1                                          | 1  | 0          | 0      | 1      | 1      | 0      | 0      | 1      | 0           | 1           | 0           |

| +3<br>V      | 1                                          | 0  | 1          | 0      | 1      | 1      | 0      | 0      | 1      | 0           | 1           | 0           |

| +2<br>V      | 0                                          | 0  | 1          | 1      | 1      | 1      | 0      | 0      | 1      | 0           | 1           | 0           |

| +V           | 1                                          | 1  | 0          | 0      | 1      | 0      | 1      | 0      | 1      | 0           | 1           | 0           |

| 0            | 1                                          | 0  | 1          | 0      | 1      | 0      | 1      | 0      | 1      | 0           | 1           | 0           |

| -V           | 0                                          | 0  | 1          | 1      | 1      | 0      | 1      | 0      | 1      | 0           | 1           | 0           |

| -2V          | 1                                          | 1  | 0          | 0      | 0      | 0      | 1      | 1      | 1      | 0           | 1           | 0           |

| -3V          | 1                                          | 0  | 1          | 0      | 0      | 0      | 1      | 1      | 1      | 0           | 1           | 0           |

| -4V          | 0                                          | 0  | 1          | 1      | 0      | 0      | 1      | 1      | 1      | 0           | 1           | 0           |

| -5V          | 1                                          | 1  | 0          | 0      | 1      | 1      | 0      | 0      | 0      | 0           | 1           | 1           |

| -6V          | 1                                          | 0  | 1          | 0      | 1      | 1      | 0      | 0      | 0      | 0           | 1           | 1           |

| -7V          | 1                                          | 1  | 0          | 0      | 1      | 1      | 0      | 0      | 0      | 0           | 1           | 1           |

| -8V          | 1                                          | 1  | 0          | 0      | 1      | 0      | 1      | 0      | 0      | 0           | 1           | 1           |

| -9V          | 1                                          | 0  | 1          | 0      | 1      | 0      | 1      | 0      | 0      | 0           | 1           | 1           |

| -10<br>V     | 0                                          | 0  | 1          | 1      | 1      | 0      | 1      | 0      | 0      | 0           | 1           | 1           |

| -<br>11<br>V | 1                                          | 1  | 0          | 0      | 0      | 0      | 1      | 1      | 0      | 0           | 1           | 1           |

| -<br>12<br>V | 1                                          | 0  | 1          | 0      | 0      | 0      | 1      | 1      | 0      | 0           | 1           | 1           |

| -<br>13<br>V | 0                                          | 0  | 1          | 1      | 0      | 0      | 1      | 1      | 0      | 0           | 1           | 1           |

Table 2: swtiching states of 27 CHBMLI combinations that generate the required Twenty Seven level output signals

Т 1

6

0

0

0

0

0

0 0 0

0

0

0

0

0

0

0

0

0 0

0

1

1 1 0 0 0 1 0 1 1 0

1 1

1 1

1 1 0 0

1 1

1 1

1

0 0 0

0

0

0 0

0 0

0 0

0 0 1 0 1 0 1 0 1 1

0 0 1 0 1 1 1

1 1

1

1

1 1

1 0 0 0 1 0 1

1 0 0 1 1 0 0 0

0

0 0 0 1 0 1 0 1 0

0 0

0

0

0

0 0

1 1

0

0 1 0 1

1 1

1

0

0 1 1

0

0 0

0

0 0 -13

0

0 0 -15

1

1

0

1

1

1

-8

-9

-10

-11

-12

-14

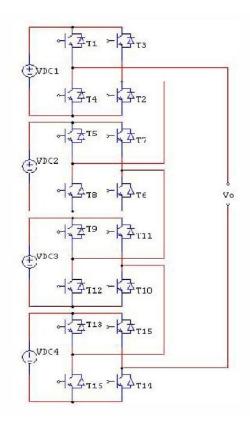

#### 2.Basic 31 Cascaded H-bridge asymtric Multilevel inverter

The 31-level cascaded Multilevel inverter circuit is seen in figure 5, which contains 16 switches with four different DC source voltages, and which must be in the following ratios:1VDC:2VDC:4VDC:8VDC. This circuit can generate up to 31 levels of output voltage, range of output voltages between +15 and -15 including zero voltage level.

Table (3) shows the appropriate Switching states and terminal output voltages of a 31-level Cascaded H-bridge Multi-level inverter.

fig.5. 31 Level Cascaded H-Bridge MLI

| T<br>1<br>5 | T<br>1<br>4 | T<br>1<br>3 | T<br>1<br>2 | T<br>1<br>1 | T<br>1<br>0 | Т<br>9 | Т<br>8 | Т<br>7 | Т<br>6 | Т<br>5 | Т<br>4 | Т<br>3 | Т<br>2 | Т<br>1 | vo |

|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----|

| 0           | 1           | 1           | 0           | 0           | 1           | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 15 |

| 0           | 1           | 1           | 0           | 0           | 1           | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 1      | 14 |

| 0           | 1           | 1           | 0           | 0           | 1           | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 13 |

| 0           | 1           | 1           | 0           | 0           | 1           | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 12 |

| 0           | 1           | 1           | 0           | 1           | 0           | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 11 |

| 0           | 1           | 1           | 0           | 1           | 0           | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 1      | 10 |

| 0           | 1           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 9  |

| 0           | 1           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 8  |

| 0           | 1           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | 7  |

| 1           | 0           | 1           | 0           | 0           | 1           | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 1      | 6  |

| 1           | 0           | 1           | 0           | 0           | 1           | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 5  |

| 1           | 0           | 1           | 0           | 0           | 1           | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 4  |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 3  |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 1      | 2  |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 1  |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0  |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | -1 |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 0      | 1      | -2 |

| 1           | 0           | 1           | 0           | 1           | 0           | 1      | 1      | 1      | 0      | 0      | 1      | 1      | 0      | 0      | -3 |

| 1           | 0           | 1           | 1           | 1           | 0           | 0      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | -4 |

| 1           | 0           | 1           | 1           | 1           | 0           | 0      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | -5 |

| 1           | 0           | 1           | 1           | 1           | 0           | 0      | 1      | 1      | 0      | 0      | 0      | 1      | 0      | 1      | -6 |

| 1           | 0           | 0           | 0           | 1           | 0           | 1      | 0      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | -7 |

Table 3: Switching States and Terminal Voltage of 31 Level Cascaded H-Bridge

#### **Simulation Results**

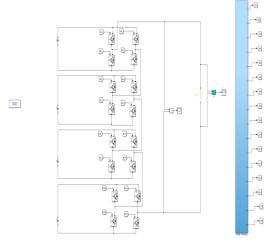

The circuit of the cascading asymmetric multi-level inverter with 31 levels and 27 levels was built based on the MATLAB /Simulink program.

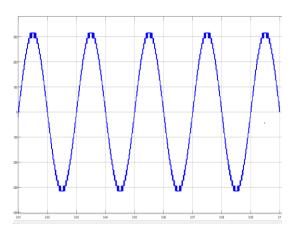

The MATLAB / Simulink model of a 31 Level- Cascaded H - Bridge Inverter is shown in Figure 6.Where Four cells with unequal voltages were used and R value is 100 connected to the output of the inverter. The values of voltages are: VDC1=8, VDC2=16, VDC3=32, and VDC4=64. This model can generate 31 levels only in output voltage as shown in figure(7).

Figure.6 simulation model of 31 Level-Cascaded H-Bridge inverter

Fig 7.output voltage for 31 levels

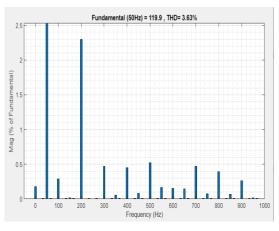

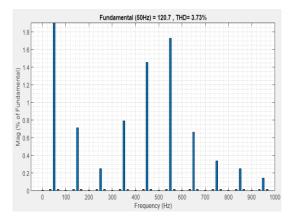

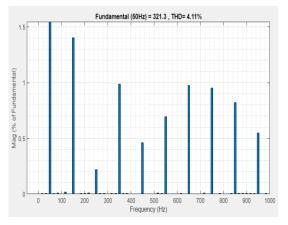

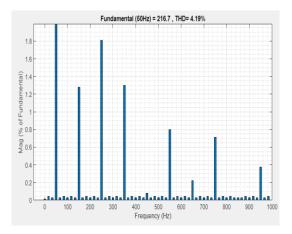

phase disposition sinusoidal pulse-width Modulation and phase opposition disposition sinusoidal Pulse Width Modulation techniques were used where the total harmonic content was analyzed by using fast Fourier transform analysis and was the value of THD at use (PD-PWM) as shown in the figure(8), but when using a (POD- PWM) technique, it was a value as shown in the figure(9).

Fig 8.THD in (PD-SPWM) technique for 31 levels

As for the circuit for 27, three sources of different values were used as well, values were VDC1=8, VDC2=24, and VDC3=72, the output wave contained 27 levels as shown in figure (10).

Fig 10. output voltage for 27 levels

This circuit also was analyzed in Matlab using FFT figure (11) analysis, shows the THD ratio when using the (PD-PWM) technique, and figure(12)displays THD (POD-PWM)when using the technique.

Fig(11).Total Harmonic Distortion in (PD-SPWM)for 27- level

Fig(12).Total Harmonic Distortion in (POD-SPWM) technique for 27- level

Table (4) the comparsion analysis for the 31level and 27-level under the two different techniques.

| Inverter       | No.of | THD%<br>PD- POD-<br>SPWM SPWM |      |  |  |  |  |

|----------------|-------|-------------------------------|------|--|--|--|--|

| level switches |       | PD-                           | POD- |  |  |  |  |

|                |       | SPWM                          | SPWM |  |  |  |  |

| 27             | 12    | 4.11                          | 4.19 |  |  |  |  |

| 31             | 16    | 3.63                          | 3.73 |  |  |  |  |

Table 4 THD for 27 and 31 levels

#### Conclusion

This paper presents a THD analysis of 31 CHB-MLI and 27 CHB-MLI. Phase-Shift SPWM and phase-opposition- SPWM techniques were used to compare the performance of the 27level and 31-level cascading H-bridge topologies. The simulation results show that 31 levels were better than 27-levels using (PD-SPWM) and (POD-SPWM) techniques because 31 levels have lower THD in both techniques. Simulation results also show that THD in 31-levels and 27 levels are lower in (PD-) SPWM) compared to POD-SPWM technology. In addition, by increasing the number of levels, the total harmonic distortion will decrease and the waveform has become closer to the sine wave.

## REFERENCES

- M. Hagiwara, and H. Akagi, "Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 1737-1746, July 2009.

- [2] M. S. I. Tarek, A. Siam, M. Zia, and M. M. Rahman, "A novel five-level inverter topology with reactive power control for grid-connected PV system," in 2018 International Conference on Smart Grid and Clean Energy Technologies (ICSGCE), 2018, pp. 101–105.

- [3] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," *IET Power Electronics*, vol. 4, no. 8, pp. 951–958, 2011.

- [4] P. Ratnani, S. S. Shaha and A. G. Thosar, "Simulation of Five-Level Inverter with Sinusoidal PWM Carrier Technique Using MATLAB/Simulink," pp. 367-376, 2014.

- [5] P. A. Arbune and A. Gaikwad, "Comparative Study of Three level and Five level Inverter," *International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering*, vol. 5, no. 2, pp. 681–686, 2016.

- [6] F. Wang, Y. Le, M. Wang, S. Yu, and Z. Xing, "Power Balance Control Scheme of Cascaded H- Bridge Multilevel Inverter for Grid-Connection Photovoltaic Systems," in 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), 2016, pp. 1539–1545. Sharma and R. K. Randhawa, Β. "COMPARATIVE STUDY OF MULTI LEVEL INVERTERS BASED ON THE OUTPUT TOTAL HARMONIC DISTORTION," International Research Journal of Engineering and Technology (IRJET), vol. 8, 2021.

- [7] I. H. Shanono, N. R. H. Abdullah, and A. Muhammad, "A Survey of Multilevel Voltage Source Inverter Topologies, Controls and Applications," *International Journal of Power Electronics and Drive Systems*, vol. 9, no. 3, p. 1186, 2018.

- [8] M. F. Kangarlu and E. Babaei, "A Generalized CascadedMultilevel Inverter Using Series Connection of Submultilevel Inverters," *IEEE transactions on power electronics*, vol. 28, no. 2, pp. 625–636, 2012. doi: 10.1109/TPEL.2012.2203339.

- [9] N. S. Hasan, et al., "Reviews on multilevel converter and modulation techniques Renew," *Renewable and Sustainable Energy Reviews*, vol. 80, pp. 163–174, 2017.

- [10] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation technique," *IET Power Electronics*, vol. 4, no. 8, pp. 951– 958, 2011.

- [11] A. Nordvall, "Multilevel Inverter Topology Survey," Thesis for the Degree of Master of Science, pp.1-78, 2011.

- [12] R. Pari, R. Sivakumar, S. Sivaranjani and Murugesan M., "Different Types of Multilevel Inverter Topologies - A Technical Review," *International Journal of Advanced Engineering Technology*, vol. 7 no. 1, pp. 149-15, 2016.

- [13] H. S. Maaroof, H. Al-Badrani, and A. T. Younis, "Design and simulation of cascaded H-bridge 5-level inverter for grid connection

system based on multi-carrier PWM technique," *IOP Conference Series: Materials Science and Engineering*, vol. 1152, no. 1, p. 012034, May 2021.

- [14] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for highpower applications," *IEEE transactions on industry applications*, vol. 36, no. 3, pp. 834– 841, 2000.

- [15] I. Sarkar and B. G. Fernandes, "Modified Hybrid Multi-Carrier PWM Technique for Cascaded HBridge Multilevel Inverter," in *IECON 2014-40th Annual Conference of the IEEE Industrial Electronics Society*, 2014, pp. 4318–4324.

- [16] A. K. Ranjan, D. V. Bhaskar, and N. Parida, "Analysis and simulation of cascaded Hbridge multi level inverter using level-shift PWM technique," in 2015 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2015], 2015, pp. 1–5.

- [17] A. Kahwa, H. Obara, and Y. Fujimoto, "Design of 5-level Reduced Switches Count H-bridge Multilevel Inverter," *in 2018 IEEE* 15th International Workshop on Advanced Motion Control (AMC), 2018, pp. 41–46.

| Altarntive Phase Opposition Disposition | APOD |

|-----------------------------------------|------|

| phase disposition                       | PD   |

| Phase Opposition Disposition            | POD  |

| Cascaded Bridge                         | СНВ  |

| Asymmetrical multi-level inverter       | AMLI |

| symmetrical multi-level inverter        | SMLI |

| Total Harmonic Distortio                | THD  |

| Multi Level Inverter                    | MLI  |

جدول المختصرات

## دراسة مقارنة للتشوه التوافقي الكلي بين المستويين 27 و 31 لمغيرات متعدد المستويات احادى الطور

محمد على عبدالله mauom@uomosul.edu.iq

منی حسن حسین muna.20enp54@student.uomosul.edu.iq

تاريخ الاستلام:3-8-2022

جامعة الموصل - كلية الهندسة - قسم الهندسة الكهربائية - موصل – العراق

تاريخ القبول: 26-10-2022

استلم بصيغته المنقحة: 1-9-2022

الملخص

تم تفضيل استخدام المحولات متعددة المستويات ، والمعروفة أيضًا باسم MLIs ، على المحولات التقليدية نظرًا للخصائص التي تمتلكها MLIs. تتضمن هذه الخصائص أن التشوه التوافقي الناجم عن MLIs ضئيلُ للغاية ، وأن أداؤها مرضٍ. لذلك ، ظهرت المحولات متعددة المستويات كعنصر أساسي في إلكترونيات القدرة وتّم استخدامها بشكل كبير في مجموعةً واسعةً من التطبيقات الصناعية والتجارية عالية الجهد وعالية القدرة. الغرض من هذا البحث هو الاستفادة من التحليل التوافقي لاكتساب فهم أعمق لأداء مغيرات القنطري المتعاقب متعددة المستويات (CHB-MLI). حيث تم إنشاء النموذج باستخدام MATLAB / SIMULINK ، وتم إجراء مقارنة بين العاكس متعدد المستويات 27 و 31 مستوى (MLI) باستخدام تقنية تعديل عرض النبض الجبيي لترتيب الطور (PD-SPWM) وتقنية (POD-SPWM). وفقًا لنتائج عمليات المحاكاة ، كأن 31 مستوى أفضل من 27 لأن المحتوى التوافقي الكلي ل 31 مستوى أقل من المحتوى التوافقي الكلي ل 27 مستوى ، وأفضل نتيجة تم الحصول عليها خلال هذه الدراسة كانت لـ 31 مستوى في التكنولوجيا (PD-SPWM) ، حيث كانت النسبة المئوية للتشوه التوافقي الكلي صغيراً مقارنة بباقي النتائج ، حيث كانت القيمة تساوي 3.63٪. الكلمات الدائه

مغير متعدد المستويات (MLI)،تعديل عرض النبض الجيبي لترتيب الطور (PD-PWM) ،التشوه التوافقي الكلي (THD)،مغير متعددة المستويات القنطري المتعاقب (CHBMLI)، مغير متعدد المستويات غير المتماثل (AMLI).